Battery_ZERObase

[반도체 공정] 4. Etching Process (식각 공정) 본문

김성호 교수님의 <기초반도체공정> 유튜브 강의를 정리한 내용에 삼성 반도체 뉴스룸, SK 하이닉스 뉴스룸, 딴딴's 반도체사관학교, 렛유인 [반도체 이론편] 내용 참조하여 공부한 것임을 밝힙니다.

* Etching Procss

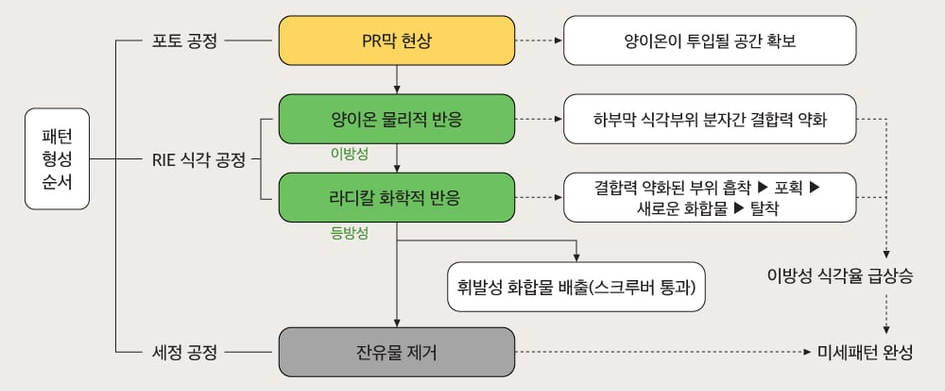

: Photo공정에서 정의된 영역의 하부 박막을 제거해서 원하는 반도체 회로 형상을 만드는 기술

∴ '포토공정에서 만들어진 모양 그대로 식각을 할 수 있는지' 가 식각 능력을 판단하는 중요한 기준

* Photo공정에서 정의한 모양대로 박막 형상을 만드는 방법?

① Etching

↪ 화학 반응을 이용하여 감광제 마스크에 의해 가려지지 않고 노출된 하부 물질을 제거하는 방법

화학반응의 결과물이 (습식 식각의 경우) 물에 녹지 않거나,

(건식 식각의 경우) 휘발성 반응물을 형성하지 않는 물질은 Etch 불가!

② Lift-off

↪ 감광제 마스크 위에 박막을 증착한 후, 감광제를 제거하여 감광제가 없었던 부위에만 박막을 남기는 방법

③ Damascene (상감법)

↪ 하부물질을 식각 가능한 박막으로 형성한 후 감광제 마스크 작업 및 식각을 진행하여 홈(Trench)을 만들고,

이 홈에다가 패턴 형성을 원하는 박막을 채워 넣고 홈 위의 물질을 갈아내서 없애는 patterning 방식

: Etchant를 이용해 Wafer에 존재하는 Layer를 선택적으로 제거

: Wet / Dry Etching 으로 분류 가능

* Wet Etching = Wafer를 chemical 용액에 담그는 방식 (->batch)

화학용액과 film 사이에 일어나는 화학반응으로 Etching 진행(Chemicla Etching) = 등방성

film과 직접적으로 화학반응 하기 때문에 selectivity가 좋음. (약 50:1)

진공장비 등이 필요하지 않으므로 저렴.

undercut 때문에, μm 이하의 pattern 식각 시에는 사용하기 어려움 -> Native Oxide 제거 공정

-> Cleaning 공정에서 사용 中...

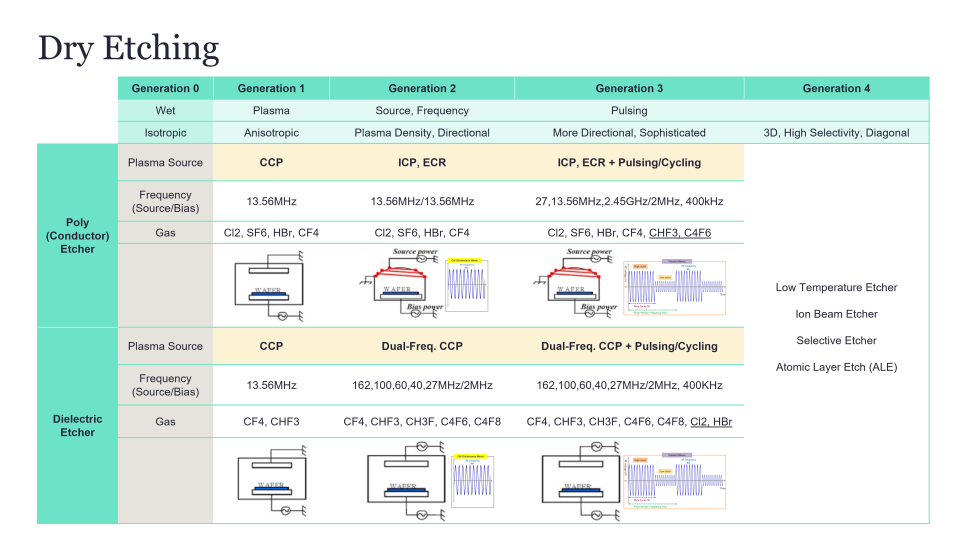

* Dry Etching = Plasma를 이용하여 물리적으로 Etching 진행 (Physical 또는 Physical+Chemical Etcing) = 비등방성

Wet etch보다 selectivity(조건마다 다름), etch rate, throughput이 좋지 않음.

미세한 패턴 식각이 가능하기 때문에, nm단위의 pattern을 식각하는데 사용

+) 종류

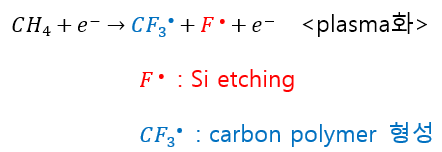

① Physical Sputtering: Plasma화 된 Ar 이온에 큰 전압을 가해 가속시킨 후, 그 에너지를 이용해

물리적인 방법으로 식각 (-> 비등방성의 profile 얻을 수 있음)

Ar이 충분한 운동에너지를 갖게 하기 위해, 낮은 진공을 유지하는 것이 중요(<10mTorr)

but, Masking layer도 함께 식각되기 때문에 selectivity가 좋지 않음. (2:1 or 1:1)

+ Etch rate이 느림(~ 10-30nm/min)

+ 이온 가속을 위한 높은 전압을 인가해야 함(High beam energy, >1 kV) ∴ selectivity와 etch rate를 향상시키기 위해, reative gas 사용(CF4, CCl4, O2)

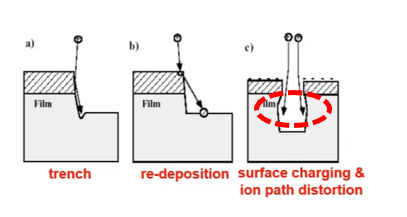

+ trench, re-deposition, surface charging & ion path distortion 의 단점도 있음

a) Trench: Plasma 이온이 PR과 만나 굴절된 상태로 film에 떨어지는 현상

b) Re-deposition: Plasma 이온이 PR을 타격하여 떨어져나온 PR이 film에

떨어지는 현상

c) surface charging & ion path distortion

1. Plasma는 (+) ion이기 때문에 mask 벽면에 (-) 전하가 쌓임.

2. mask surface의 (-) 전하로 인해 틈을 지나는 plasma가 휨.

3. 빨간 점선 영역의 plasma density가 높아지며 항아리 모양 식각

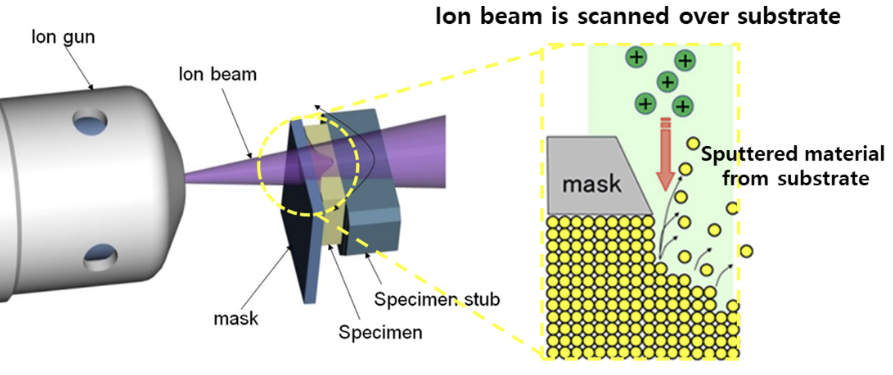

-> CF4를 사용시, side wall에 carbon polymer을 형성해 보완

:polymer가 있는 sidewall은 etching 불가 ∴Verticle한 Etch 가능

∴ Physical sputtering은 RIE를 사용할 수 없는 물질들에 한해서 사용

= Ion milling 라고도 함. ↓ ↓ ↓

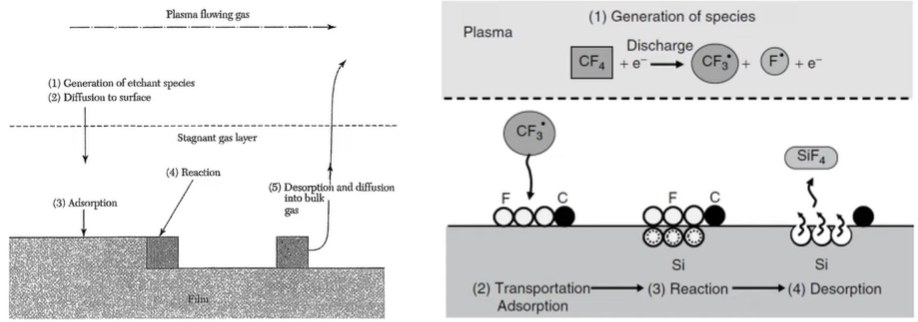

② Plasma Etching: 화학물질을 plasma화 시킨 후, plasma화 된 ion을 이용한 Chemical 반응

(-> 약간의 등방성의 profile 얻을 수 있음)

Plasma를 만들 수 있는 정도의 진공도만 만들어주면 됨(>100mTorr)

화학반응을 기반으로 하므로 selectivity 좋음 + 이온 가속 할 필요가 없는 Low beam energy

but, 화학반응 후 생성되는 byproduct가 휘발성 물질인 경우에만 사용 가능

③ Reactive Ion Etching(RIE): 가속된 이온과 화학적 반응 모두를 이용 (-> 등방성 조절 가능)

ㄴ> 가속된 이온 = 물리적 식각 기능 X, 화학 반응을 도와주는 기능 O

이온 가속을 위한 낮은 진공 필요 (<10mTorr)

화학반응을 기반으로 하므로 selectivity 좋음 + 약간의 이온 가속인 Medium beam energy

-> 대부분의 반도체, 절연체, 몇몇 금속물질(Al, Cu, Ti, W, Cr)까지 식각 가능

but, etch rate이 높지 않아, 수 μm 정도 제거에만 사용

+ 등방성이므로, 완벽히 수직한 profile 얻을 수 없음

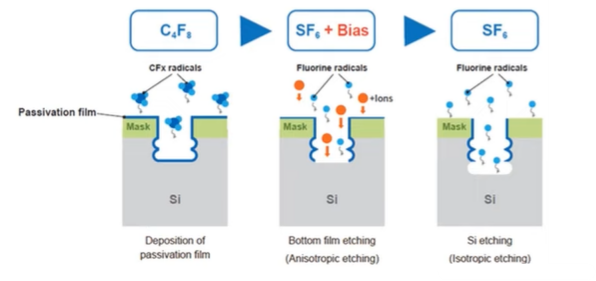

∴ 더 깊고, 수직한 etch를 하기 위해 Deep RIE(=Bosch process) 사용 -> TSV 공정

가장 많이 사용되는 Plasma Etch에 대한 더보기

↓ ↓ ↓

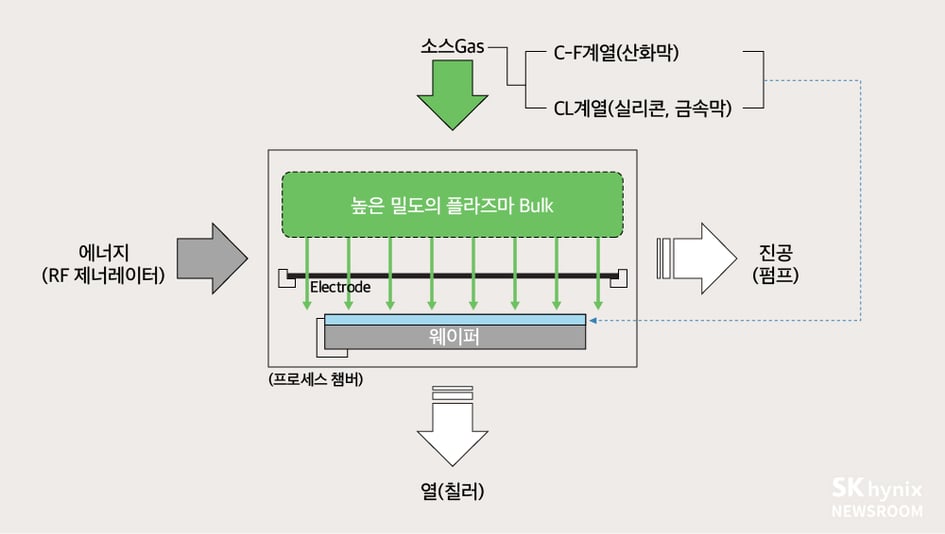

* Plasma 형성 방법

1. CCP/ICP란?

: Plasma를 인가하는 에너지 Type(DC/AC)에 따라

-> 직류 plasma

-> 교류(RF) plasma = 플라즈마를 형성하는 방법에 따라, CCP와 ICP로 구분

* CCP (Capacitively Coupled Plasma)

: 2개의 전극판 사이에서 축전 전기장을 형성시켜 Plasma를 만는 용량성

: 전극 방향대로 e-의 방향이 형성되며, 전극으로 들어가는 전자에 의해 e- loss가 심

: Plasma가 Density와 DC Voltage로 정의되므로, 따로 두 변수는 control 불가

: F 계열로, Oxide나 Nitride Etching 시 사용

* ICP (Inductively Coupled Plasma)

: 전류가 흐르는 도선 주위에 RF를 인가하면 수직한 방향으로 유도자기장 형성 -> 전기장을 통해 Plasma 형성

(plasma 외곽으로 코일을 감아 놓은 구조인 유도성)

: e- 운동 경로가 전극 내부에서 잘 격리되어 CCP보다 전자 loss를 줄일 수 있음

= High plasma density 구현 가능 -> High-Tech로 tkdyd

: 회전운동을 하다보니 donut 모양의 plasma가 형성되며 plasma의 uniformity ↓

: Cl 계열로, 높은 Aspect Ratio(고단차비)를 안정적으로 형성

2. Plasma Etching 공정 변수

=> Lam사의 Flex GX를 기준으로 한 Oxide etching을 가정..

: Gas, Pressure, Power, Temp

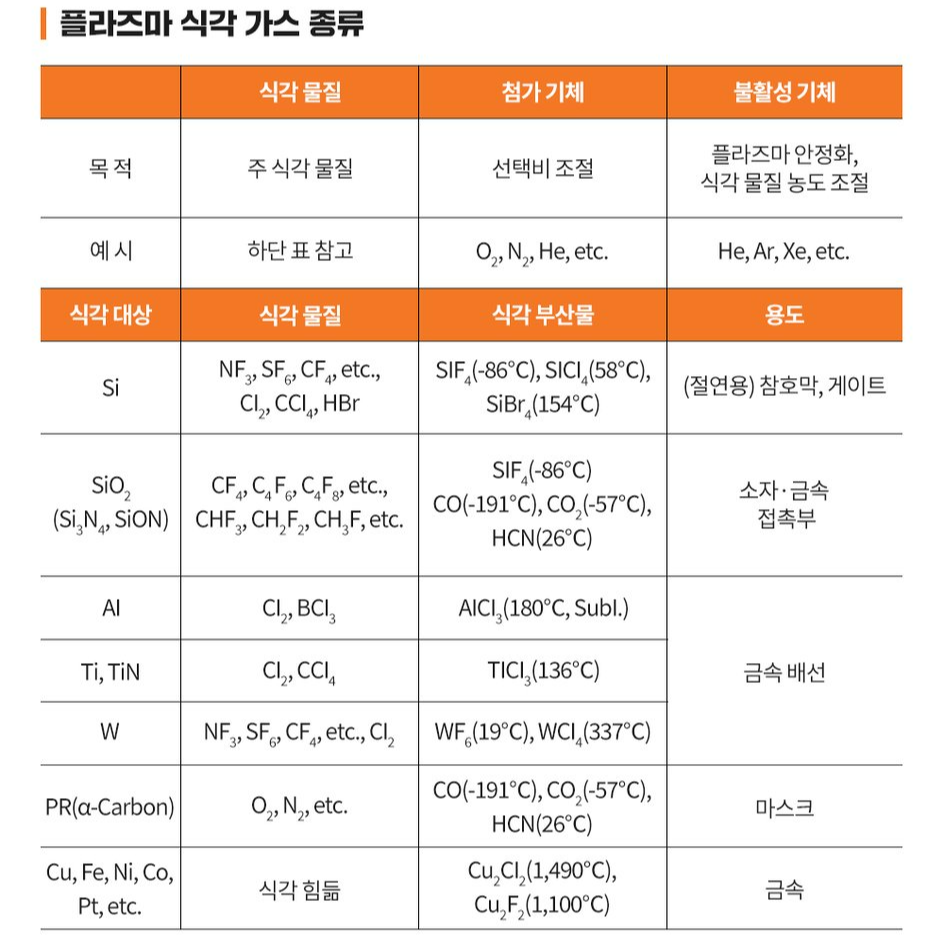

① Gas

: main gas = C4F8, C4F6, O2, Ar, COS, NF3, CHF3, CF4, CH2F2, CH3F, N2, O2...

(Center/Middle/Edge로 나누어 주입해서 chamber내 일정한 분위기 조성)

: side gas = O2, C4F8, C4F6, CH2F2

(화학적으로 반응성이 큰 원소인 할로겐원소(F, Cl, Br)를 source로 많이 이용)

+) O2 등의 gas line이 여러개인 이유? = 주입하는 gas양의 오차를 줄이기 위해!

(뿌려주는 gas의 오차는 0.5~1% 내로)

ex. O2 주입되는 양이 400, 2000으로 2개일 경우, 600을 주입하고 싶을때에는

400 line으로 맞추어주는 것이 더 정확한 양의 gas를 주입할 수 있음.

ex. O2 2000은 waferless O2 cleaning시 사용

② Pressure

: Pump (Rotary Vain pump+Turbo pump(TMP))

- Rotary Vain Pump: by-product를 제거해 주므로, 쌓는 단수가 높아질수록 중요성 大

- Turbo pump(TMP): 공기를 밀어내어 더 높은 진공도를 가능하게 도와줌

③ Power

- Source power : 플라즈마를 생성하는 power (60MHz)

- Bias power : 플라즈마를 substrate로 끌어옴 (2MHz)

∴ 많이 쌓을수록, bias power를 높여주어야 함.

: 각 장비마다 다른 Inpedence를 matcher가 맞추어 power 전달 (100단 기준 Max = 10000W)

(200단의 경우, 30000~35000W)

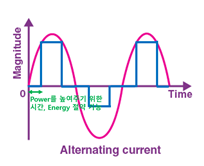

+) Pulsing기능: ion(C+, F-)이 side wall에 붙는 것을 방지하기 위한 목적

: Source power와 Bias power를 반복적으로 ON/OFF

cf) Bias power에는 보통 pulsing을 사용하는데, TEL사에서는 DC를 사용한다. 그 이유는??

-> 목표 전압까지 도달하는 시간이 작으므로, 그만큼의 cost 손실 발생 save 가능하기 때문에

④ Temp

: Plasma에 의해 wafer온도가 올라가므로,열화 현상(wafer wiggling)이 발생함.

ㄴ> 열화현상이란? : 절연체가 내외부적인 영향에 따라 화학적 및 물리적 성질이 좋지 않아짐.

∴ 사용하는 화학약품의 최적 반응 온도에 맞게 + 해당 recipe의 모든 wafer가 같은 공정온도에서 반응되도록 온도 조절 !

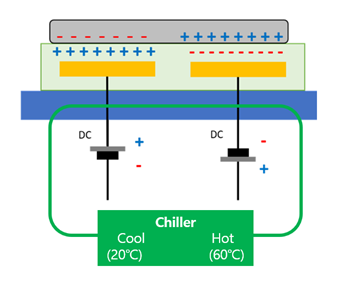

: ESC 하부에 Chiller에서 Cool, Hot 잘 섞어서 정확한 온도 set -> Wafer 뒤로 back He을 주입하여 wafer의 온도 조절

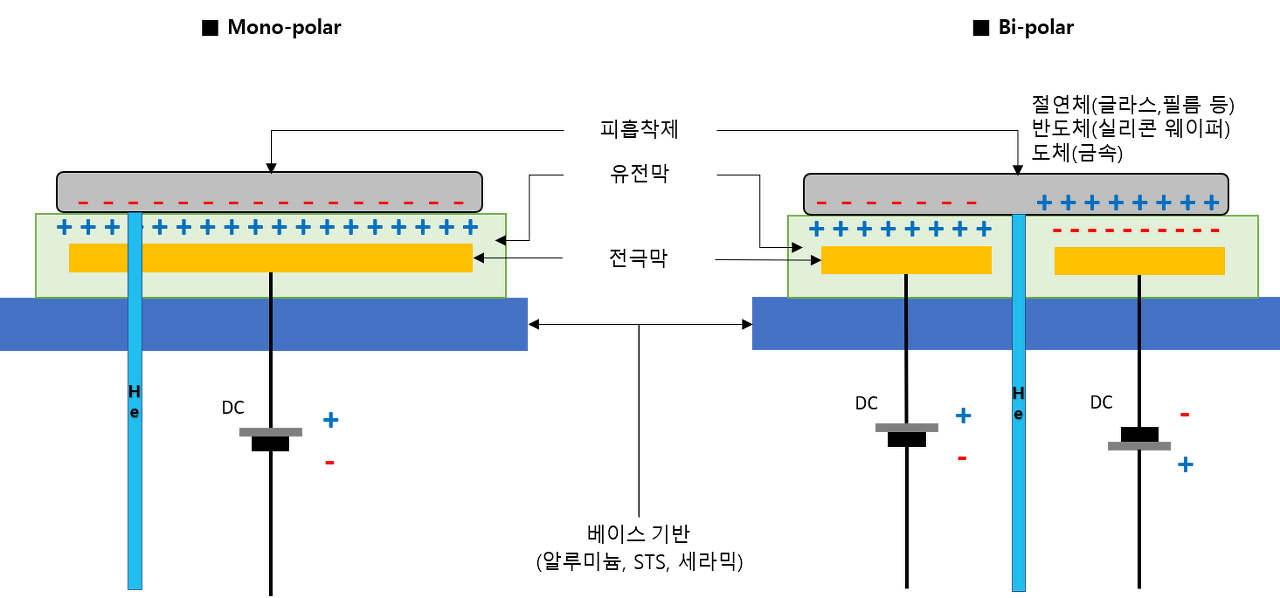

cf) ESC란?

: Electro Static chuck = chucking force(정전기적 힘)로 wafer가 공정 진행 중 흔들리지 않도록 고정해주는 역할

접촉에 의한 입자오염 문제가 없고, 진공환경에 상관없이 사용 가능

-> Unipolar ESC: 하나의 전압만을 인해주는 ESC

-> Bipolar ESC: 두 개의 전압을 같이 인가해주는 ESC

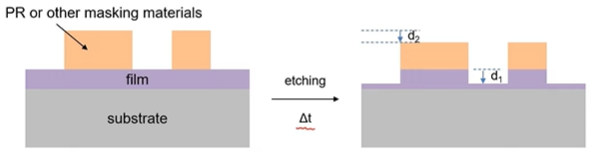

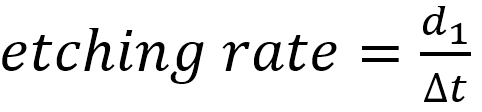

* Etching process의 성능을 나타내는 지표

① Etching rate: 식각이 진행되는 동안 웨이퍼표면으로부터 타겟 재료가 제거되는 속도 (Å/min)

: Etchant gas, 챔버 구성, target 재료의 특성 등의 여러 요인들에 의해 결정

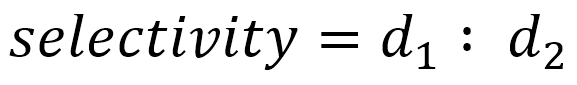

② Selectivity: 원하는 film만 식각할 수 있는 능력 (다른 물질들 간의 식각률 차이의 비율)

: film이 제거되는 동안, mask가 모두 식각되면 안됨.

" mask 식각 두께(d_2) << film 식각(d_1) " 여야!

ex) physical etching은 2:1, 1:1... << chemical etching은 20:1, 50:1...

-> Wet Etching = Si/SiO2와 같은 소재의 특성이 결정

-> Dry Etching = PR과 target 재료와의 식각률 차이의 비율

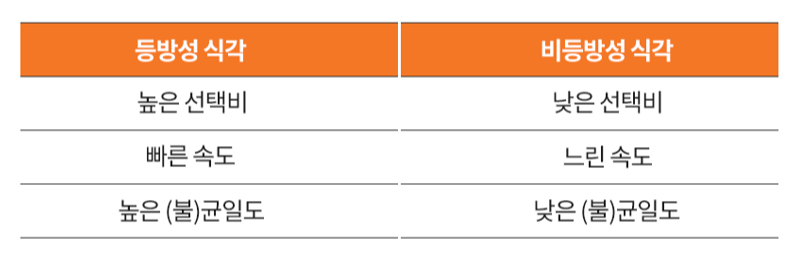

③ Etching profile: Etching 공정을 마친 후, Etch된 결과물의 모습

: Isotropic = Etch rate이 수직/수평 모든 방향에서 동일

Masking layer 안쪽으로 etching이 진행 가능 (Over etch ↓ & Undercut ↔)

-> Wet Etching(Pure chemical reaction)

: Anisotropic = 한 방향으로만 식각 (수직 방향의 etch rate >> 수평 방향의 Etch rate)

-> Dry Etching(Ion-assisted etching)

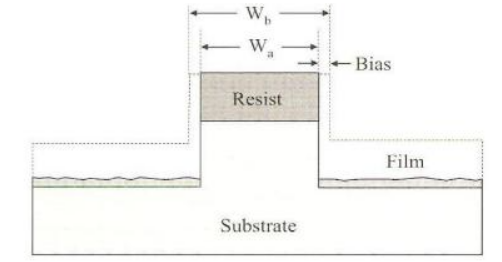

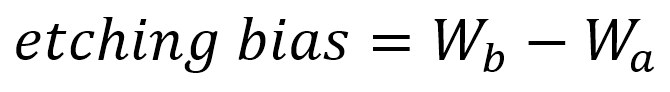

④ Etching bias: 식각 하고자 설정한 pattern의 폭과 실제 Etching 후 얻은 pattern의 차이

: Etch 전/후, PR선폭의 변화량

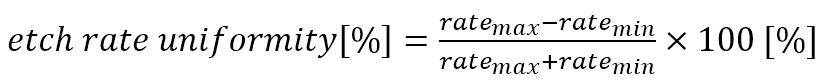

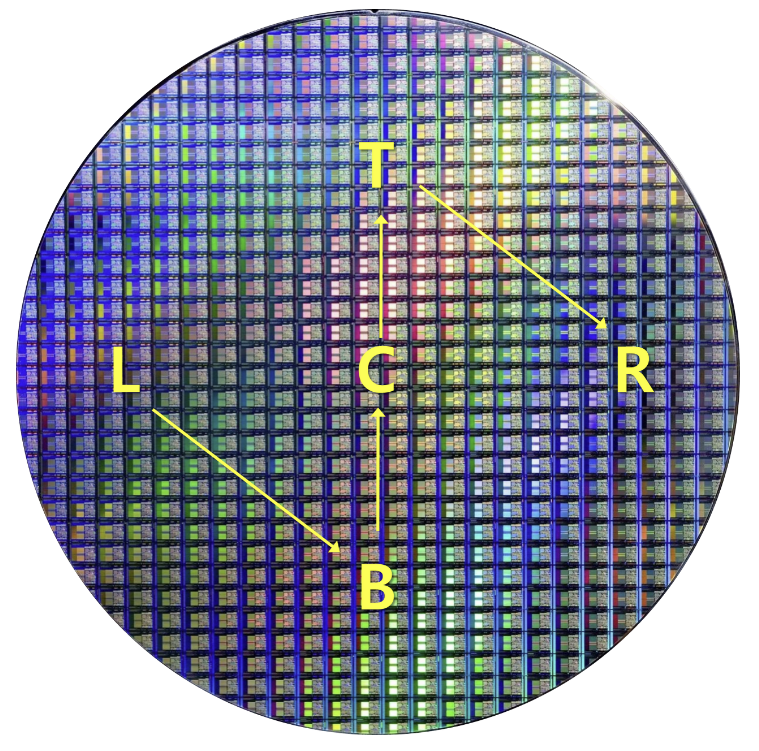

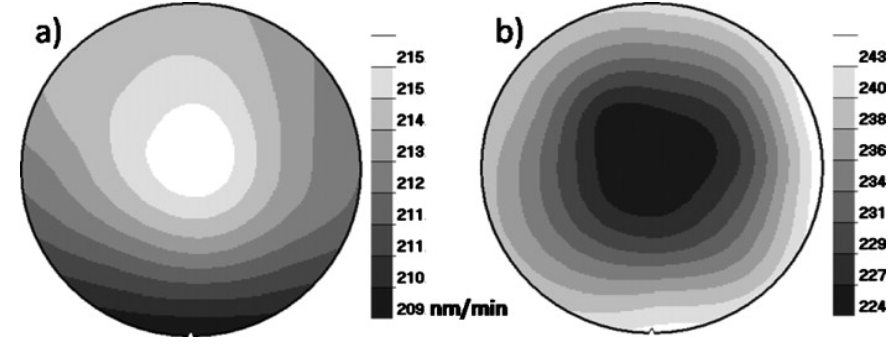

⑤ Uniformity: 각 위치에 따른 Etching rate 의 균일도 (-> 수율과 직결되는 매우 중요한 공)

: 약 9개의 point 정도의 두께를 측정함으로써 균일한 식각이 이루어졌는지 확인

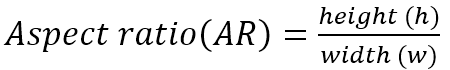

⑥ Aspect Ratio(AR): 박막이 특정 단차가 있는 profile일 경우, 단차의 width와 height의 비율

: 소자 demension이 작아지면서 AR이 커져야 하기에, etching 기술의 중요성 大

+ 높은 AR의 profile을 cover할 고도의 증착 기술도 요구되고 있음.

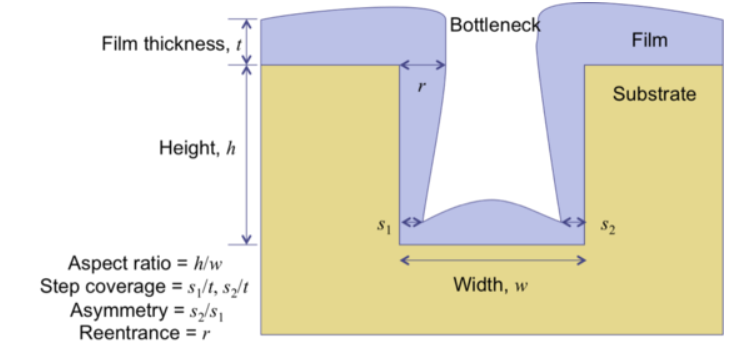

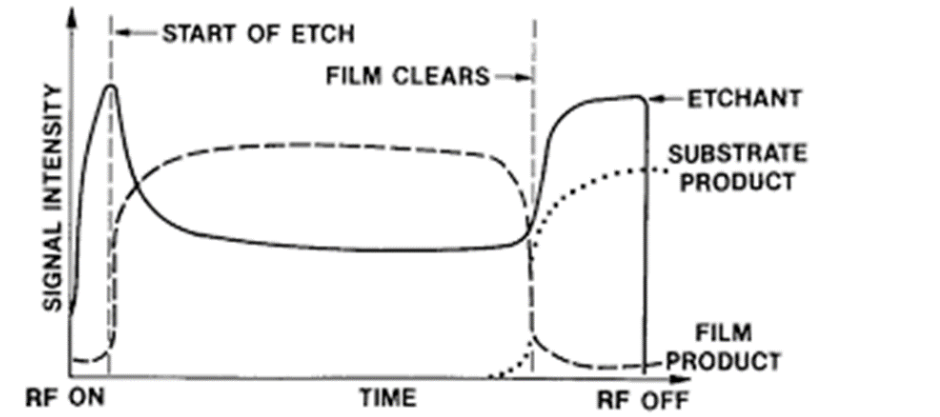

⑦ End point detection(EPD): Etching 시 원하는 target 막질이 제거되었는지 확인하는 방법

: Wafer 상의 지점별로 깎이는 식각의 깊이가 다르기 때문에 EOP(End of Point) 설정 중요!

1. OES(Optical Emission Spectroscopy, 방출분광법): Plasma 등의 광원으로부터 발생된

에너지에 의해 여기된 원자가 기저상태로 이동할 때 방출하는 빛을 관측함으로써

빛의 파장으로부터 원소의 정성 또는 빛의 세기를 통해 원소를 정량하는 방법

2. RF파의 전류, 전압을 모니터링

3. Etch 시, 발생하는 gas 성분을 분석

'반도체' 카테고리의 다른 글

| [반도체 공정] 3. Photolithography process (포토 공정) (0) | 2023.07.10 |

|---|---|

| [반도체 공정] 1. 반도체란? 반도체 공정에 사용되는 기초 지식 (0) | 2023.07.08 |